## **Avant-propos**

Le préfixe « nano », tiré du latin « nanus » qui signifie nain, est aujourd'hui très employé dans de nombreux domaines scientifiques. C'est à partir du XIX<sup>e</sup> siècle que les nanosciences, regroupant les sciences des matériaux à l'échelle nanométrique, ont suscité de nombreux travaux de recherches. Pour l'aspect « technologique », c'est à la fin du XX<sup>e</sup> siècle, plus précisément en 1974, que Norio Taniguchi, de l'Université des sciences de Tokyo (Taniguchi 1974) associe pour la première fois le terme nano à la technologie. La définition de la nanotechnologie est consignée dans le rapport du World Technology Evaluation Center (Roco et al. 2011): « La nanotechnologie est le contrôle de la matière à l'échelle nanométrique, au niveau atomique et moléculaire, située dans un ordre de grandeur allant de 1 à 100 nm, afin de créer des matériaux, des composants et des systèmes ayant des propriétés et des fonctions fondamentalement nouvelles en raison de leur petite structure. » Aujourd'hui, les nanosciences et nanotechnologie étant des champs scientifiques en forte émergence, les définitions de ces deux termes peuvent différer en fonction de la considération purement scientifique, philosophique ou même politique (Hingant et Albe 2010; Monino 2021). Dans le modèle linéaire « science en amont d'où applications en aval », les deux termes peuvent être mis en opposition. Ce modèle unidirectionnel semble aujourd'hui trop simpliste. Il est plus juste d'associer les deux thématiques et donc utiliser l'acronyme NST pour les nanosciences et nanotechnologies (Jouvenet 2012). Ce terme NST permet de mettre en évidence les complémentarités mutuelles de la nanoscience et de la nanotechnologie, et ainsi de repousser les frontières de la connaissance.

« Ce qui est nouveau, ce n'est pas le fait que les NST travaillent dans un contexte d'application (c'était déjà le cas de la science et de l'ingénierie des matériaux ; ou encore de la science des surfaces dès les années 1970). Ce n'est pas non plus le fait qu'elles travaillent à l'échelle nanométrique (c'est le cas de la chimie depuis toujours). C'est le fait que les NST participent à faire advenir des objets individualisés définis

comme "nano-objets" par leurs fonctionnements à l'échelle nanométrique. » (Loeve et Guchet 2015)

REMARQUE. Ce terme « nano-objets », définissant un objet individuel à l'échelle nanométrique (entre 1 et 100 nm), sera utilisé tout au long de cet ouvrage.

## Remerciements

Les auteures tiennent à remercier Madame Sandrine Froissart et Monsieur Xavier Larose pour les mesures réalisées au microscope électronique à balayage, ainsi que Monsieur Florent Lallemand et Monsieur Thomas Delaroque pour leurs contributions. Monsieur Hugues Murray a contribué à l'élaboration du modèle analytique du mode nano-MIS. Elles tiennent à souligner le soutien de Monsieur Wilfrid Prellier, directeur du Laboratoire CRISMAT UMR 6508 de Caen. Elles sont très reconnaissantes du support de l'Université de Caen (Unicaen), de l'école d'ingénieur Ensicaen et du CNRS. Les entreprises caennaises Murata, NXP et Presto Engineering ainsi que l'Institut CARNOT « énergie et systèmes de propulsion » et la région Normandie ont soutenu ces travaux à travers le financement de projets de recherche.

## Introduction

La miniaturisation, l'intégration de multiples fonctions, la réduction de la consommation d'énergie des composants microélectroniques et le respect des ressources naturelles sont actuellement les quatre points fondamentaux à considérer lors de la conception et la réalisation de systèmes microélectroniques fortement intégrés. Le dispositif microélectronique est le résultat de multiples étapes de fabrication. Il se compose d'une ou de plusieurs puces fonctionnelles au cœur d'un boîtier ou d'un système d'encapsulation. Ainsi, le dispositif intégré est l'aboutissement des étapes de conception, de réalisation, d'optimisation et de fabrication associant divers matériaux primaires ou de synthèse. Les constituants des dispositifs et leur fabrication seront introduits d'une manière rapide dans cette introduction pour définir certains termes et pour donner le contexte des études de microscopie à force atomique faisant l'objet des autres chapitres de cet ouvrage.

En industrie, la fabrication du composant microélectronique est généralement séparée en deux grandes étapes : la réalisation de la ou des puce(s) microélectronique(s) fonctionnelle(s), le *front-end*, et la mise en boîtier et/ou l'encapsulation du système, le *back-end*.

- Front-end: la conception du composant microélectronique commence par le choix des matériaux de base. Aujourd'hui, les wafers de silicium sont majoritairement utilisés. Par multiplication de motifs micro- ou nanométrique, le procédé de front-end comprend le dopage du semiconducteur, la photolithographie, les gravures sèches et humides pour créer les structures. Les dépôts de couches conductrices, isolantes et semiconductrices complètent le procédé. Une fois les différents motifs microélectroniques réalisés, les tests électriques sont effectués afin de vérifier la fonctionnalité et les spécifications des produits.

— Back-end: pour protéger les puces de l'environnement extérieur et pour adapter les connexions pour l'assemblage des systèmes, les étapes du back-end ont pour objectif de passiver le wafer, de découper les puces élémentaires et d'encapsuler le système dans un boîtier et/ou dans un système d'encapsulation (packaging). Ainsi sont assurées la protection thermique, électrique et mécanique, et l'adaptation des composants pour les assemblages de dispositifs à plus grande échelle.

Dans l'objectif de réduire la taille et la consommation des dispositifs conçus, l'industrie de la microélectronique a connu depuis le début des années 2000 une forte révolution, en passant du composant discret (un composant = une fonction) aux dispositifs fortement intégrés. Cette forte intégration, principalement motivée par la multiplication de systèmes connectés pour le grand public, a débuté avec le déploiement de la 3<sup>e</sup> génération de réseau de communication international (3G) en 2002. Depuis, l'impact de la demande grand public sur la stratégie industrielle n'a cessé d'augmenter pour concevoir et produire de nombreux systèmes connectés et de petite taille, c'est-à-dire fortement intégrés. Nous pouvons citer bien sûr les smartphones, mais aussi tous les dispositifs radio fréquence (RF) développés pour de nombreux domaines pour la communication, la sécurité, les divertissements, sans oublier les dispositifs pour les applications médicales et la mobilité.

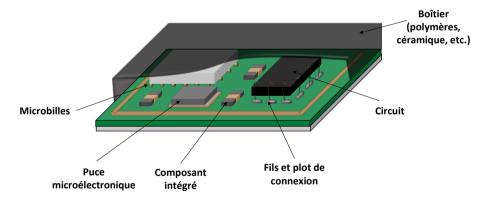

**Figure 1.** Schéma d'un dispositif microélectronique intégré contenant une puce, des composants discrets et deux circuits

Lors de la conception du dispositif, l'objectif est de définir le système correspondant au mieux à l'application, pour un coût le plus réduit possible. Le système d'encapsulation est ainsi conditionné par le concept de *Smaller Faster Lighter Denser*  *Cheaper* (Robert 2014). En plus de ces fonctions premières, le système doit respecter l'environnement et les normes en vigueur.

Les étapes de back-end dans la fabrication d'un dispositif électronique ont pour objectif de protéger des différents éléments et d'assurer les performances souhaitées lorsque le composant sera utilisé dans son application. Plusieurs puces et/ou composants discrets peuvent ainsi être intégrés pour former le dispositif (figure 1). Dans la suite de cet ouvrage, nous utiliserons le terme « puce » pour désigner un ou plusieurs composants fabriqués sur un même substrat. Plusieurs puces peuvent être assemblées et contactées pour former un circuit avant d'être encapsulées. Les stratégies d'assemblage sont nombreuses et différentes, selon le produit et les applications visés. Néanmoins, une tendance très claire s'est dessinée ces dernières années, vers une co-intégration de plus en plus importante en termes de nombre de composants, tout en proposant une diversification des fonctions au sein d'un même dispositif. Cette tendance implique donc l'emploi de matériaux hétérogènes, c'est-à-dire des matériaux avec des propriétés électriques, thermiques et mécaniques potentiellement très différentes (Lee et al. 2011; Lau 2018). Les fonctions de l'encapsulation sont nombreuses, principalement : la protection mécanique et électrique des éléments du dispositif, la transmission des signaux électriques entre les éléments et également avec le monde extérieur, et la gestion des flux thermiques internes, voire éventuellement le refroidissement local (figure 2). Le système d'encapsulation est donc l'élément qui permet de relier l'échelle submicronique de la puce à l'échelle macroscopique du dispositif.

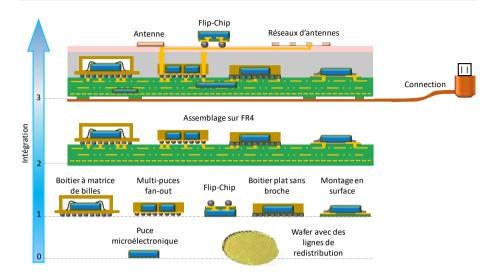

En microélectronique, le terme *packaging* représente et englobe toutes les étapes de fabrication permettant de réaliser les systèmes d'encapsulation et boîtiers. Il existe plusieurs niveaux de *packaging*, partant de l'encapsulation simple de la puce à la protection du circuit jusqu'au dispositif microélectronique. Nous pouvons les décrire en quatre niveaux :

- le niveau 0 : protection de la puce microélectronique elle-même ;

- le niveau 1 : conception d'un boîtier simple contenant une ou plusieurs puces ;

- le niveau 2 : l'assemblage des modules entre eux ;

- le niveau 3 : connexions des différents systèmes entre eux et connexions pour la communication extérieure.

À chaque niveau, la conception et l'optimisation du *packaging* sont primordiales, car elles peuvent influencer les performances électriques finales du produit. De très nombreuses stratégies de *packaging* sont développées pour s'adapter à chaque type d'application, la figure 2 illustre quelques exemples pour les quatre niveaux.

Figure 2. Illustration des 4 niveaux d'intégration du packaging

COMMENTAIRE SUR LA FIGURE 2.— Le niveau 0 concerne la puce elle-même ou le wafer, au niveau 1 les types de boîtiers sont dits simples. Au deuxième niveau, les composants sont reliés entre eux (un exemple d'assemblage est dessiné) et le niveau 3 consiste à réaliser le dispositif avec son système de connexion et d'encapsulation en rajoutant éventuellement des éléments sur le boîtier.

REMARQUE. Inscrits dans les NST, la connaissance et le comportement de la matière à l'échelle de la puce et/ou du dispositif déterminent les propriétés du produit microélectronique. À ces échelles micro et nanométriques, le microscope à force atomique (AFM) est un équipement métrologique de pointe, adapté aux petites dimensions et aux études des propriétés locales de la matière.

Pour le contrôle au cours des procédés de fabrication de tels dispositifs et les études de fiabilité du produit, une connaissance fine des propriétés locales de la matière est nécessaire. Depuis plus de 30 ans, la technique par microscopie à force atomique a montré sa capacité à répondre à de telles problématiques et à accéder aux propriétés des composants tout au long de leur vie. Ainsi, l'objectif de cet ouvrage est de démontrer les différentes possibilités de caractérisation par AFM. Nous allons voir que la maîtrise du nano-objet (pointe-échantillon) est critique pour déterminer avec justesse les caractéristiques de la matière lors de la mesure par AFM. Au chapitre 1, la technique par AFM sera introduite pour son utilisation classique, la mesure de topographie de surface. Dans ce premier chapitre, le mode mécanique permettant de déterminer le module d'Young de la matière sera également présenté pour un cas

d'étude relatif au *packaging*. Le chapitre 2 présente les techniques de mesures de trois modes électriques, basées sur l'AFM. Les trois modes considérés sont : le *Scanning Capacitance Microscopy* (SCM), le *Scanning Spreading Resistance Microscopy* (SSRM) et le *scanning Microwave Impedance Microscopy* (sMIM). Pour chaque mode, l'analyse fine du contact pointe-échantillon, en utilisant un échantillon de calibration, permettra d'exposer les méthodologies de mesure associées, avec un aspect métrologique. Et pour finir, au chapitre 3, trois cas d'études, illustrant l'intérêt de ces modes, seront présentés : la détermination de la structure d'une capacité fortement intégrée, l'analyse AFM électrique d'un transistor MOS pour une application RF et la caractérisation d'une diode de commutation (diode PIN).